# **REPP 2021**

November 3, 2021

# Heterogeneous Integration Roadmap An Overview

William (Bill) Chen

WR (Bill) Bottoms & Ravi Mahajan

In Collaboration with Heterogeneous Integration Roadmap (HIR) Technical Working Groups Team

# Agenda

- REPP Symposium Goal

- Covid 19 & Digital Transformation

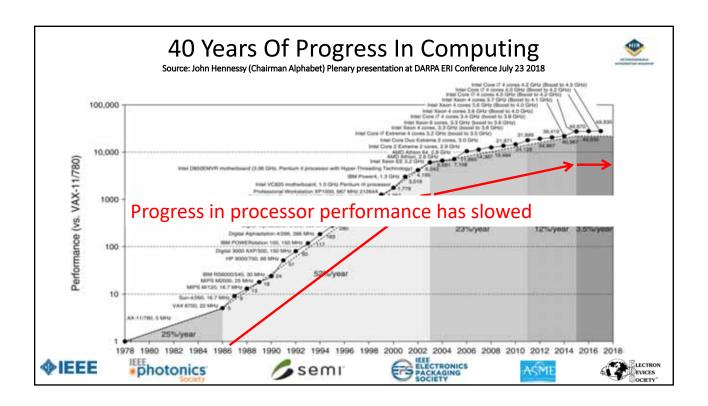

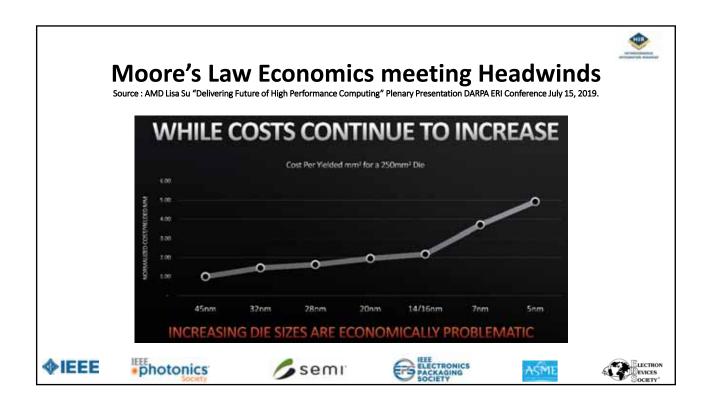

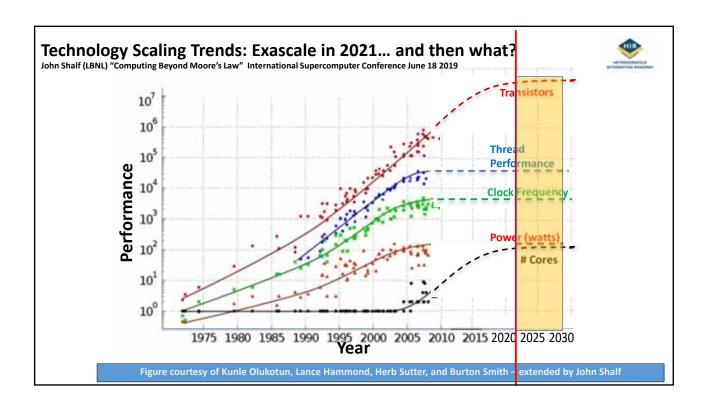

- Coming to End of Technology Scaling

- Heterogeneous Integration Roadmap

- Innovations in Heterogeneous Integration Rising Everywhere

- Summary

## **REPP 2021 Symposium Goals**

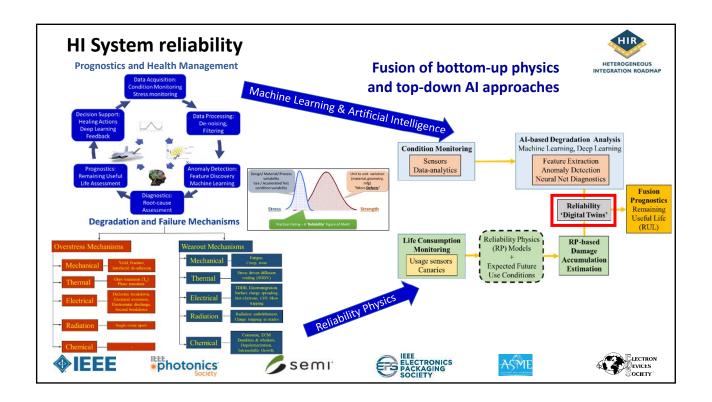

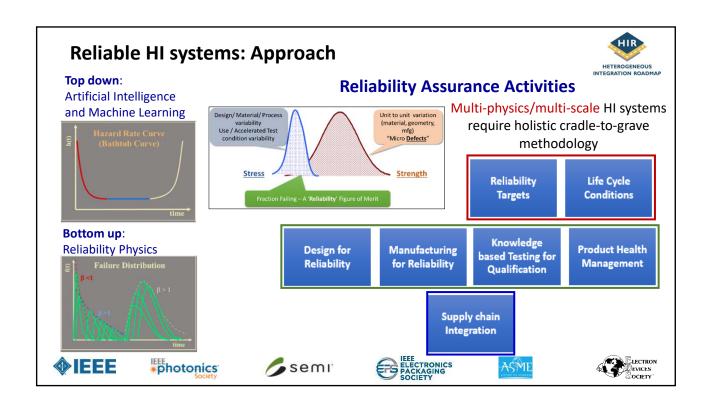

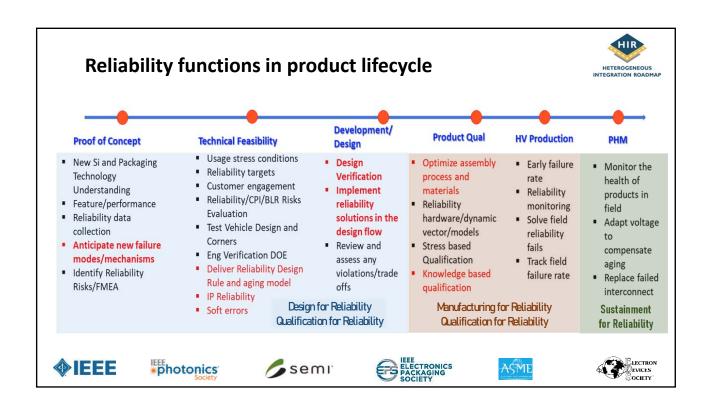

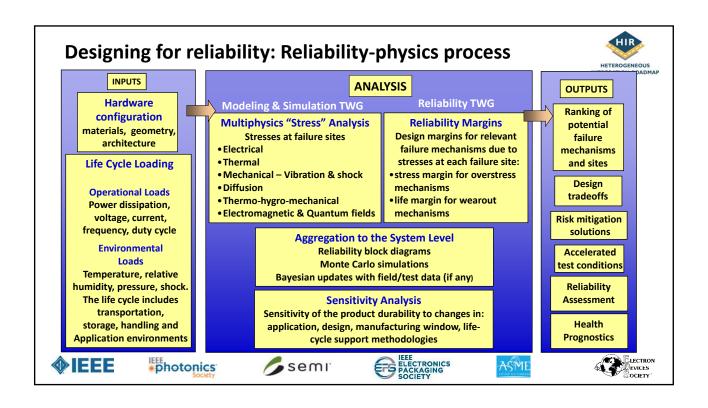

- This symposium will focus on quantitative methods for reliability, accelerated testing and

probabilistic assessment of the useful lifetime of Heterogeneous Integration components

including electronic, photonic, and MEMS and sensor packages and sub-systems across different

markets & applications.

- Includes failure modes, mechanisms, testing schemes, accelerated testing, stress levels, environmental stresses and machine learning methods for developing and fielding reliable products for the market places.

- The intent is to bring together electrical, reliability, materials, mechanical, and computer

engineers and applied scientists from around the world to address the state-of-the-art and future

directions in all the interconnected fields of electronic and photonic packaging, with an emphasis

on various reliability-related science & technology: design-for-reliability, manufacturing, reliability

modeling, accelerated testing, real-time sustainment (prognostics and health management) and

digital twins.

2

## **COVID-19 Pandemic**

- As we go through the pandemic, we are seeing millions of infections & staggering loss of life, but also incredible heroism, sacrifice, and resilience.

- The rapid advancement of vaccine science, and comprehensive vaccines deployment are tremendous achievements in global collaboration

- While the Delta Covid Variants are surging, we are hopeful in rapid growth of vaccination. We are optimistic to meet face to face once more not too far into the future

# **Technology Roadmapping History**

#### 1991

World's first Open Source Technology Roadmap, the National Technology Roadmap for Semiconductors (NTRS) sponsored by the US Semiconductor Industry Association (SIA).

#### 1998

NTRS expanded forming the first Global Technology Roadmap. Europe, Japan, Taiwan, and Korea joined. It was renamed International Technology Roadmap for Semiconductors (ITRS).

#### 2014

The benefits of Moore's Law scaling diminishing and decision was made to end ITRS.

#### 2016

The last edition of the ITRS was published July 8, 2016

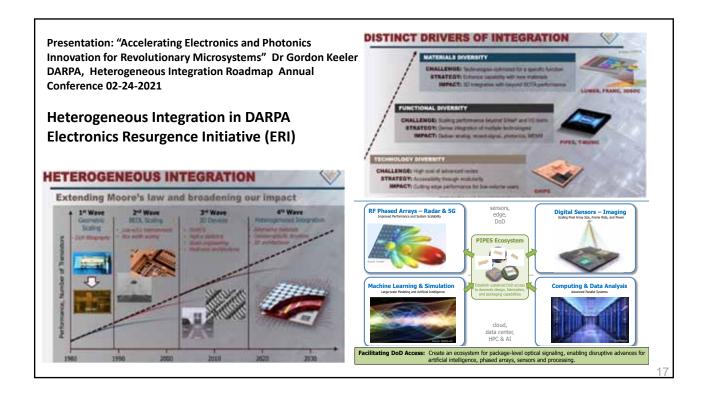

#### IEEE Press Release 10-10-2019

PISCATAWAY, N.J.--(<u>BUSINESS WIRE</u>)--IEEE, the world's largest technical professional organization dedicated to advancing technology for humanity, today announced the 2019 release of the <u>Heterogeneous Integration Roadmap (HIR)</u>, a roadmap to the future of electronics identifying technology requirements and potential solutions. The primary objective is to stimulate pre-competitive collaboration among industry, academia and government to accelerate progress. The roadmap offers professionals, industry, academia and research institutes a comprehensive, strategic forecast of technology over the next 15 years. The HIR also delivers a 25-year projection for heterogeneous integration of emerging devices and materials with longer research-and-development timelines

10

### **Heterogeneous Integration Roadmap (HIR)**

Launched 10-10-2019 24 chapters 590 Pages Free download Download Link https://eps.ieee.org/technology/hete rogeneous-integration-roadmap

- Sponsored by 3 IEEE Societies (EPS, EDS & Photonics) together with SEMI & ASME Electronics & Photonics Packaging Division

- Comprehensively covering microelectronics technology ecosystem

- Articulates state-of-the-art Advances in Technology & Science, **Future directions, Significant roadblocks & Potential solutions**

- HIR is the Knowledge Roadmap & Knowledge Supply Chain for the Heterogeneous Future

- The 2021 HIR Edition will be launched December 2021

"Cramming More Components onto Integrated Circuits," Gordon Moore, Electronics, pp. 114-117, April 19, 1965.

particular array."

"VIII. DAY OF RECKONING

design and construction, should allow the

"It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected. The availability of large functions, combined with functional

-----The total cost of making a particular system function must be minimized. To do so, we could amortize the engineering over several identical items, or evolve flexible techniques for the engineering of large functions so that no disproportionate expense need be borne by a

manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically."

Revisiting Dr Godon Moore's words today.

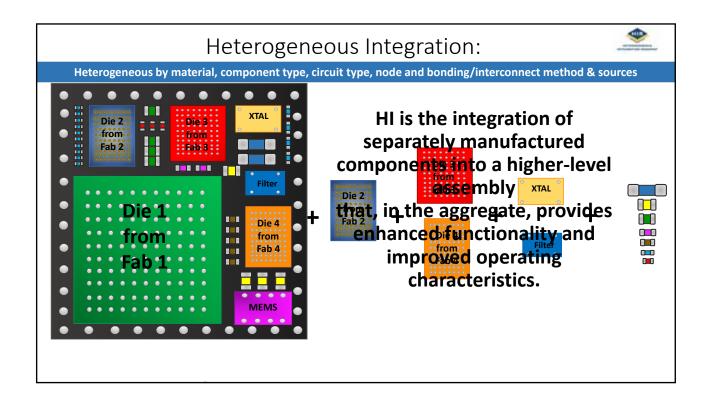

HI is the integration of separately manufactured components into a higherlevel assembly (including SIP & Chiplets) that, in the aggregate, provides enhanced functionality and improved cost, performance & time to market

A visionary message for Chiplets, System-in-Package & Heterogeneous Integration

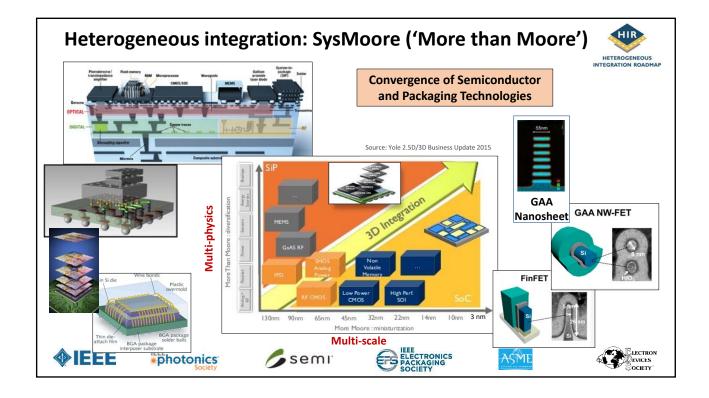

# Heterogeneous Integration Roadmap

An Application Driven Roadmap

### **Market/System Applications**

- High Performance Computing & Data Center

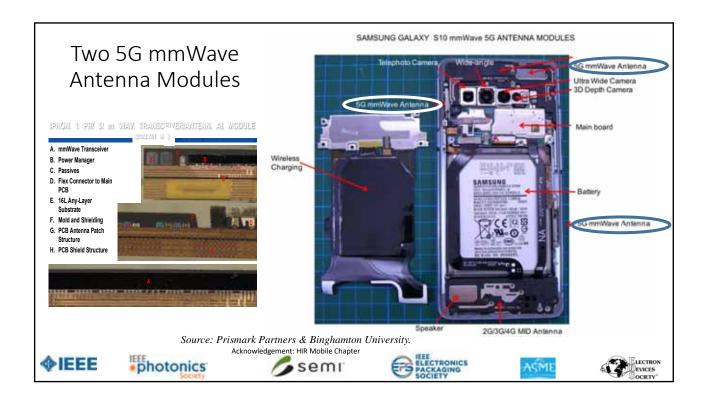

- Mobile

- Medical, Health & Wearables

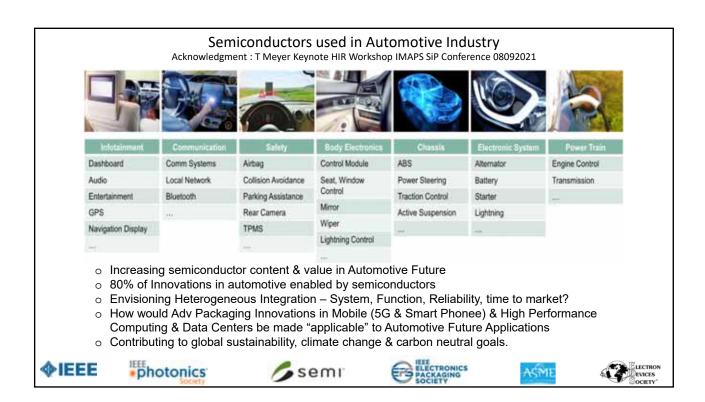

- Automotive

- loT

- Aerospace & Defense

# Heterogeneous Integration Components

- Single Chip and Multi Chip Integration (including Substrates)

- Integrated Photonics

- Integrated Power Electronics

- MEMS & Sensor integration

- 5G Communications & Beyond

#### **Cross Cutting Technologies**

- · Materials & Emerging Research Materials

- Emerging Research Devices

- Test

- Supply Chain

- Security

- Thermal Management

- Reliability (new chapter for 2021)

#### **Integration Processes**

- SiP

- 3D +2D & Interconnect

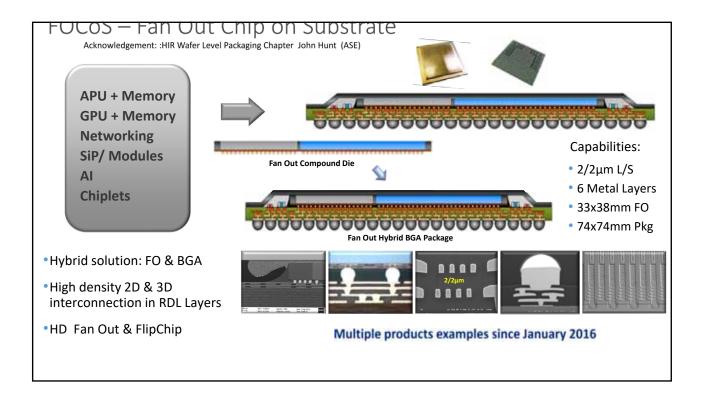

- · WLP (fan in and fan out)

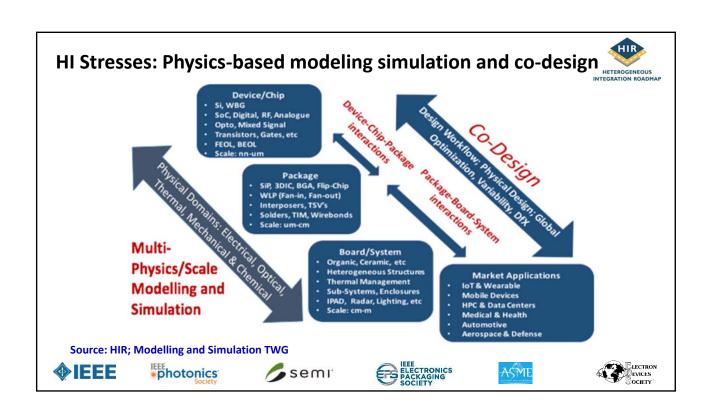

#### **Co-Design & Simulation**

Co-Design & Simulation – Tools & Practice

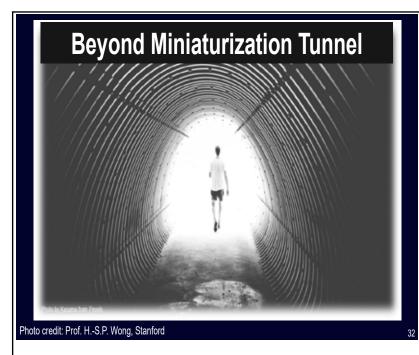

At 2020 ERI Conference the Plenary Speaker, (Prof Philip Wong, Stanford University, and TSMC Chief Scientist) gave talk "Future is System Integration. He illustrated semiconductor research near the end Moore's Law like a person walking out of a long tunnel seeing green field & sun light.

During Moore's Law time the single focus is miniaturization towards the next set of nodes.

As one emerges from the miniaturization tunnel, opportunities for research outlook & innovations becomes infinitely brighter and broader.

Photo Source: S. Mitra, HIR Symposium Feb 24, 2021

# Innovations Rising everywhere!!

Explorations of new system & package architectures, new materials & new devices, and innovative solutions to design, cost, security, time to market

Virtual Reality

AI & ML for everything

Integrated Photonics

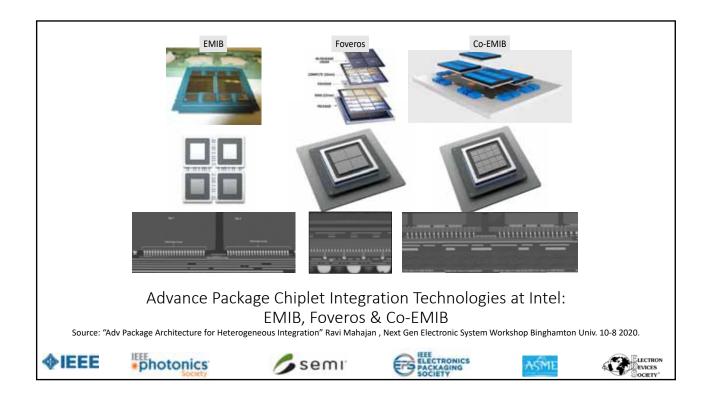

WL & PL Fan Out Si Bridge & 3D

Brain wave control of complex systems

Nanotube transistors

Qbits

AI + Co-Design & Co-Simulation

Photon Computers

materials design

Implantable sensors for health care

Plasmonic Devices

Robotics everywhere

A . . . . . . . . . . . . . . D . . . I'

# **Summary**

- We are at a unique period in time where the global convergence of technology cnaos & business disruption are suddenly joined by the Covid 19 Pandemic still spreading around the world.

- There is immense need for a pre-competitive technology roadmap addressing future vision, difficult challenges, potential solutions.

- Heterogeneous integration (e.g SiP & Chiplets) is a powerful technology direction for system/subsystem integration.

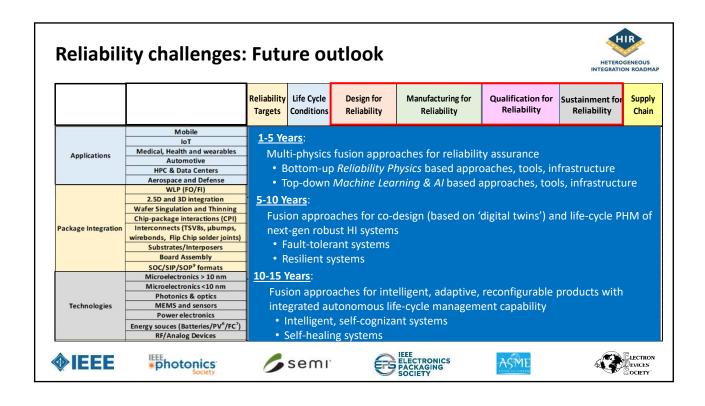

- Reliability is essential while complex for all market applications from lot, automotive, 5G communications to data centers, advanced aerospace & defense products.

- We are looking forward to collaborations & innovations in reliability Science empowered by AI & M L, in this important area for the Heterogeneous Integration Roadmap.

IEEE REPP Symposium, HIR Workshop, Nov 11, 2021

# Heterogeneous Integration Systems: Ensuring Reliability

Abhijit Dasgupta

Center for Advanced Life Cycle Engineering (CALCE)

University of Maryland, College Park, MD 20742

dasgupta@umd.edu

## **Acknowledgment:**

Richard Rao (Marvell Corporation), Shubhada Sahasrabudhe (Intel)

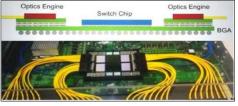

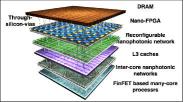

## **Heterogenous integration**

- Electronic (Passive/Active)/Photonic/MEMS/Sensor devices

- Digital; Analog; Logic; Memory; Power; RF

- System, Package (Chiplets) and Wafer levels, including Interconnects and Substrates

- 2.5D and 3D Packaging technologies

Photonic switching devices and SIP concepts

https://eps.ieee.org/images/files/HIR 2019/ HIR1 ch09 photonics.pdf

**IEEE**

## HIR Technical Working Groups

#### HI for Market Applications

- Mobile

- IoT

- Medical, Health & Wearables

#### Automotive

- High Performance Computing & Data Center

- Aerospace & Defense

#### **Heterogeneous Integration Components**

- Single Chip and Multi Chip Packaging (including Substrates)

- **Integrated Photonics**

- **Integrated Power Electronics**

- MEMS & Sensor integration

- RF and Analog Mixed Signal

#### **Cross Cutting topics**

- Materials & Emerging Research Materials

- **Emerging Research Devices**

- Interconnect

- Test

- **Supply Chain**

- Security

- Thermal Management

#### Integration Processes

- SiP

- 3D +2.5D

- WLP (fan in and fan out)

#### Design & Reliability

- Co-Design

- **Modeling** and Simulation

Reliability

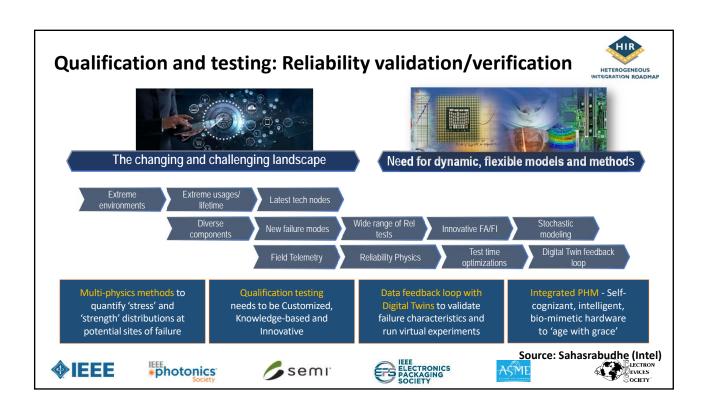

#### HIR Reliability is a cross-cutting TWG: Cross-TWG interactions Life Cycle Reliability Life Cycle Qualification for Manufacturing for Sustaining for Supply Design for Reliability **Economics** Targets Conditions Reliability Reliability Reliability Chain & Cost Mobile; IoT; MHW; Mobile; IoT; MHW; Mobile; IoT; MHW; Mobile; IoT; MHW; Automotive; HPC; **Applications** Automotive; HPC; Automotive; HPC; Automotive; HPC; Aerospace Aerospace Aerospace Aerospace Electromigration; Materials; Co-Design and Simulation; SCMCI; WLP; 2.5D/3D; WLP; 2.5D/3D; WLP; 2.5D/3D; WLP; 2.5D/3D; vlaguZ No TWGs Package Interconnects; SIP; Interconnects; SIP; Interconnects; SIP; Interconnects; SIP; Chain TWG yet?? Integration Photonics; SCMCI; Test **SCMCI** SCMCI; Security MEMS/Sensors; Power; RF/Analog; Test Photonics: Photonics; Photonics; SiP MEMS/Sensors: MEMS/Sensors: Power: MEMS/Sensors: Power: Power; RF/Analog; **Technologies** RF/Analog; Test RF/Analog; Test Security **<b>�**IEEE \*photonics 🥏 semi ASME

## **Current members of reliability TWG:**

- 1. Abhijit Dasgupta, Univ of Maryland; dasgupta@umd.edu

- 2. Richard Rao, Marvell; richardrao@marvell.com

- 3. Shubhada Sahasrabudhe, Intel; shubhada.h.sahasrabudhe@intel.com

- 4. Willem D. van Driel; Signify; willem.van.driel@signify.com

- 5. Przemyslaw J. Gromala; Bosch; PrzemyslawJakub.Gromala@de.bosch.com

- 6. Hualiang Shi; Lyft; hualiang.shi@gmail.com

- 7. Albert Wang; Univ of California Riverside, aw@ece.ucr.edu

- 8. Pradeep Lall; Auburn University; lallpra@auburn.edu

- 9. Bo Ericsson, Ericsson, bo.e.eriksson@ericsson.com

- 10. Siva Shivashankar, Google, <a href="mailto:rsivasankar@google.com">rsivasankar@google.com</a>

- 11. SAAB rep