# **Advanced Packages and Their Reliability Challenges**

### Jason Zhang, Principal Engineer Sandeep Sane, Principal Engineer Ravi Mahajan, Fellow

## **Intel Corporation**

Acknowledgments: Ravi Mahajan, Pooya Tadayon, Sandeep Sane, Thomas Huber, Kemal Aygun, Kaladhar Radhakrishnan, Debendra Mallik, Gaurang Choksi, Rahul Manepalli, Chris Baldwin, Sergey Shumarayev, Ram Viswanath, Pat Stover, Wilfred Gomes, Gans Ganesan, Sriram Srinivasan, Ahmet Durgun, CM Jha, Weihua Tang, Upendra Sheth

# Outline

- Moore's Law, Challenge and Package Solution

- Key Drivers for Heterogeneous Integration

- Intel Advanced Package Overview

- Challenges and Opportunities

- Summary

## Moore's Law, Challenge & Package Solution

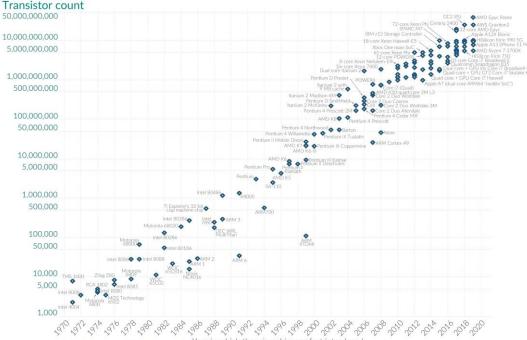

#### Moore's Law: The number of transistors on microchips doubles every two years

Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years. This advancement is important for other aspects of technological progress in computing – such as processing speed or the price of computers.

Moore's Law guides the industry to achieve higher performance and lower cost chips

Moore's Law has been challenged since its creation

Heterogeneous Integration (HI) further boosts Moore's Law

Data source: Wikipedia (wikipedia.org/wiki/Transistor\_count) Year in which the microchip was first int OurWorldinData.org – Research and data to make progress against the world's largest problems. Lice

Licensed under CC-BY by the authors Hannah Ritchie and Max Roser.

## Increased Interest in Heterogenous Integration is Driven by

Additionally, Yield Resiliency and Time to Market Advantages Make On-Package HI Attractive

## The Package is a Compact HI Platform For Several Interesting Use Cases

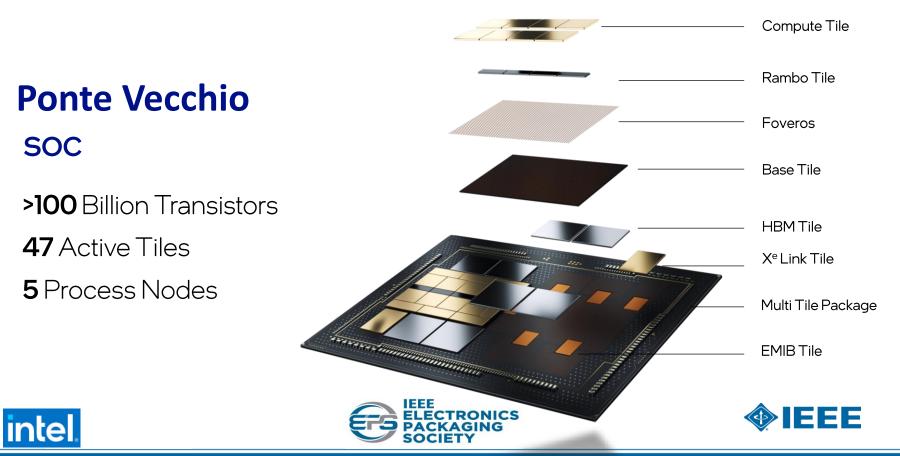

# **Intel Advanced Heterogenous Integration Packaging**

#### Embedded Multi-die Interconnect (EMIB)

#### bump pitch 55-40 micron

- first 2.5D embedded bridge solution

- die to die connection through embedded bridges in substrates

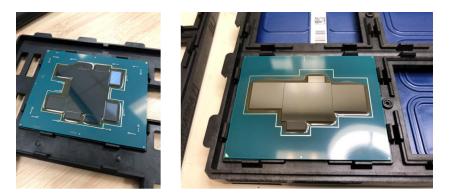

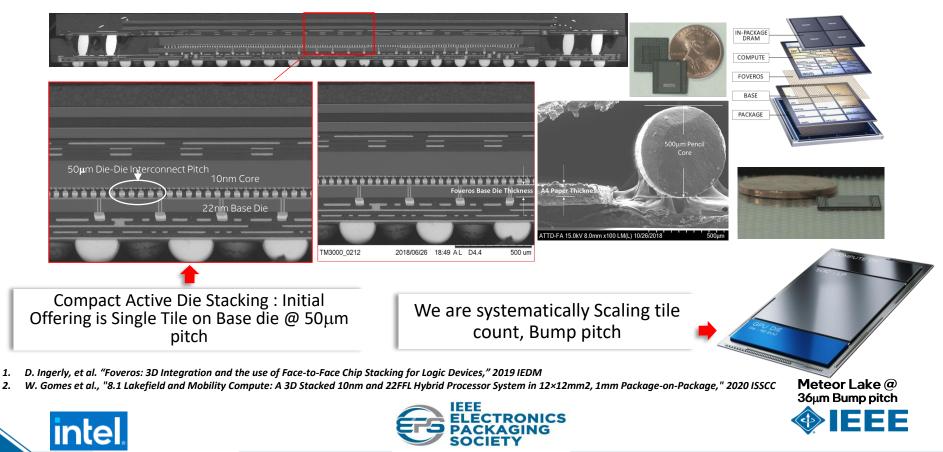

#### Foveros Technology

#### bump pitch 50-18 micron

- wafer level packaging through TSV

- first-of-its-kind 3D stacking solution

- Die to die connection through active interposer

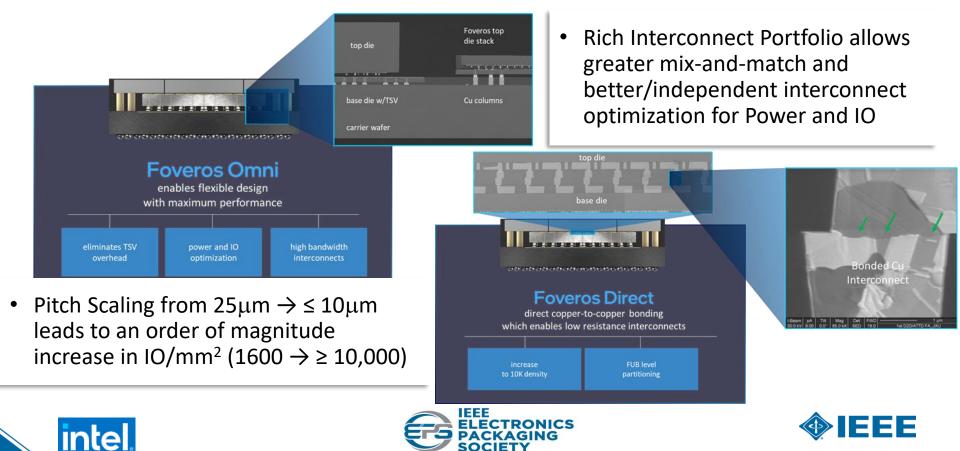

#### Foveros Omni

#### bump pitch 25-18 micron

next generation Foveros

Unbounded flexibility with performance 3D stacking technology for die to die interconnect and modular designs

#### **Foveros Direct**

#### bump pitch **≤ 10 micron**

- Direct Cu-Cu bonding for low resistance interconnects

- Blurs the boundary between where the wafer ends and the package begins

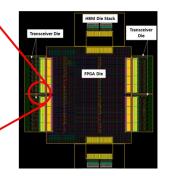

## **EMIB Technology can be combined with Foveros technologies**

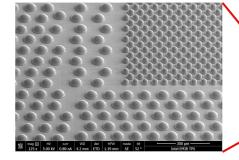

# EMIB: Embedded Multi-Die Interconnect Bridge

- Localized high-density wiring

- Multiple Bridges, Multiple Bridge Sizes and Bridge Technologies

- ➢ Bridge Mix and Match → Enhanced Design Flexibility

- Bridge silicon costs << Silicon interposer</p>

- ➢ No TSVs, Significantly less silicon area

- Die from Different Foundries

- Large Overall Die Area enabled

- > 2x areal bandwidth density

- 4x better PHY power efficiency

# **Foveros : High Density 3D Active Stacking**

# Blending Planar and 3D MCPs (EMIB + Foveros)

Sources: R Mahajen and S. Sane, "Advanced Packaging Technologies for Heterogeneous Integration", HOT CHIPS 2021

## Packaging Innovations In The Near Future: Foveros Omni and Foveros Direct

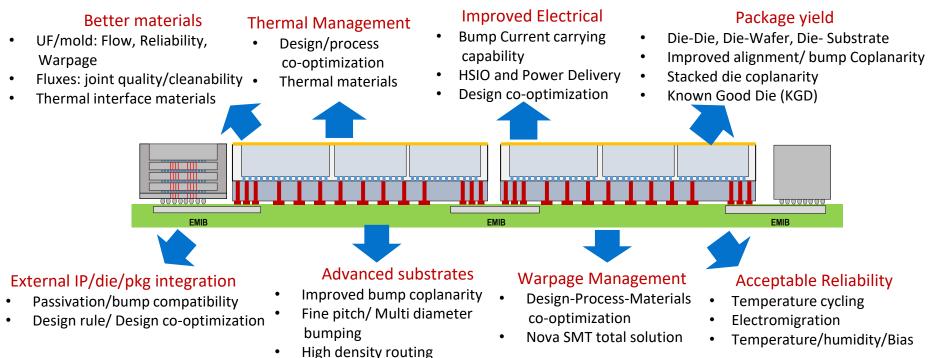

## **Challenges and Opportunities**

Equipment/ Material/Process/ Design Co-optimization key to Heterogeneous Assembly & Packaging

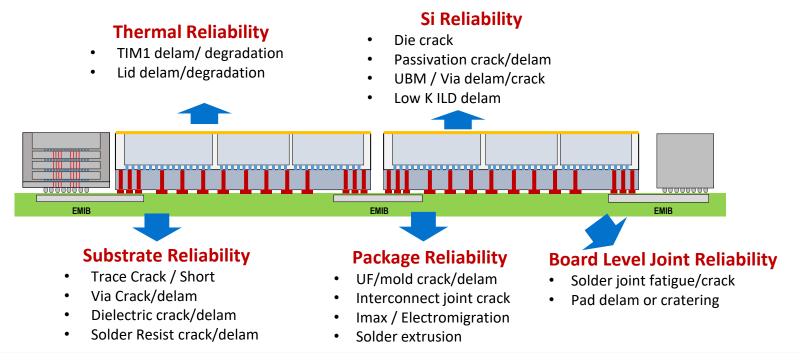

## **Reliability Challenges**

Equipment/ Material/Process/ Design Co-optimization Key to Meet Reliabilities

- Heterogenous integration is a key enabler of performance and cost moving forward

- Intel invented several advanced packaging architectures and applied them in Client, Server and Discrete Graphics products to provide unprecedented levels of Heterogeneous Integration

- The next generation of Innovations in Heterogeneous Integration will offer increased partitioning opportunities with an enhanced interconnect portfolio and significant increases in interconnect density

- Equipment/ Material/Process/ Design Co-optimization is the key to meet yield, performance, cost and reliability targets of complex advanced packages

#### Legal Notices

All product and service plans, and roadmaps are subject to change without notice. Any forecasts of goods and services needed for Intel's operations are provided for discussion purposes only. Intel will have no liability to make any purchase in connection with forecasts published in this document. Code names are often used by Intel to identify products, technologies, or services that are in development and usage may change over time. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All product and service plans and roadmaps are subject to change without notice. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

Statements in this document that refer to future plans or expectations are forward-looking statements. These statements are based on current expectations and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in such statements. For more information on the factors that could cause actual results to differ materially, see our most recent earnings release and SEC filings at www.intc.com.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others. This document contains information on products and/or processes in development.

#